- 您现在的位置:买卖IC网 > Sheet目录3876 > PIC16F639-E/SS (Microchip Technology)IC MCU FLASH 2KX14 20SSOP

Micrel, Inc.

KSZ8841-PMQL

October 2007

55

M9999-100407-1.5

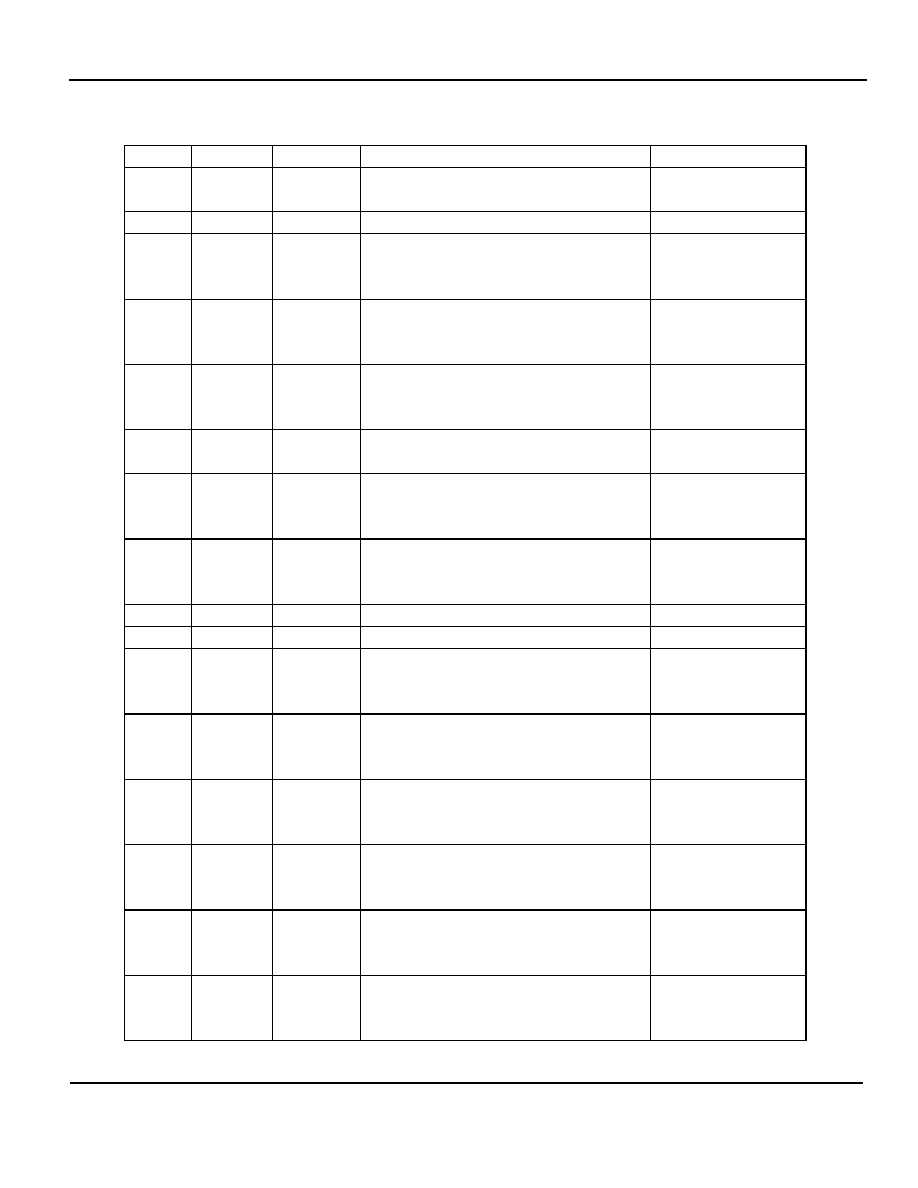

PHY 1 MII Register Basic Control Register (Offset 0x04D0): P1MBCR

This register contains the MII register control for the chip function.

Bit

Default

R/W

Description

Is the Same as

15

0

RO

Soft reset

NOT SUPPORTED

14

0

RW

Reserved.

13

0

RW

Force 100

1 = Force 100 Mbps if AN is disabled (bit12)

0 = Force 10 Mbps if AN is disabled (bit12)

P1CR4, bit 6

12

1

RW

AN enable

1 = Auto-negotiation enabled

0 = Auto-negotiation disabled

P1CR4, bit 7

11

0

RW

Power down

1 = Power down

0 = Normal operation

P1CR4, bit 11

10

0

RO

Isolate

NOT SUPPORTED

9

0

RW

Restart AN

1 = Restart auto-negotiation

0 = Normal operation

P1CR4, bit 13

8

0

RW

Force full duplex

1 = Force full duplex if AN is disabled (bit12)

0 = Force half duplex if AN is disabled (bit12)

P1CR4, bit 5

7

0

RO

Reserved

6

0

RO

Reserved

5

0

R/W

HP_mdix

1 = HP Auto MDIX mode

0 = Micrel Auto MDIX mode

P1SR, bit 15

4

0

RW

Force MDIX

1 = Force MDIX

0 = Normal operation

P1CR4, bit 9

3

0

RW

Disable MDIX

1 = Disable auto MDIX

0 = Normal operation

P1CR4, bit 10

2

0

RW

Disable far end fault

1 = Disable far end fault detection

0 = Normal operation

P1CR4, bit 12

1

0

RW

Disable transmit

1 = Disable transmit

0 = Normal operation

P1CR4, bit 14

0

RW

Disable LED

1 = Disable LED

0 = Normal operation

P1CR4, bit 15

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18LF24K22-I/SS

IC PIC MCU 16KB FLASH 28SSOP

PIC24F08KL402-I/ML

IC MCU 16BIT 8KB FLASH 28-QFN

PIC24F08KL302-I/SP

IC MCU 16BIT 8KB FLASH 28-SPDIP

PIC16LF1938-I/ML

IC MCU 8BIT FLASH 28QFN

PIC24F08KL402-I/MQ

IC MCU 16BIT 8KB FLASH 28-QFN

PIC16LF1938-I/MV

IC MCU 8BIT 28KB FLASH 28UQFN

PIC18F24K22-I/SS

IC PIC MCU 16KB FLASH 28SSOP

PIC16F1938-I/ML

IC MCU 8BIT FLASH 28QFN

相关代理商/技术参数

PIC16F639-I/P

功能描述:8位微控制器 -MCU 4kb 128 RAM 12 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F639-I/SO

功能描述:8位微控制器 -MCU 4kb 128 RAM 12 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F639-I/SS

功能描述:8位微控制器 -MCU 4kb 128 RAM 12 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F639-I/SS

制造商:Microchip Technology Inc 功能描述:8-Bit Microcontroller IC

PIC16F639T-I/SO

功能描述:8位微控制器 -MCU 4kb 128 RAM 12 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F639T-I/SS

功能描述:8位微控制器 -MCU 4kb 128 RAM 12 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F648A-E/ML

功能描述:8位微控制器 -MCU 7KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F648A-E/P

功能描述:8位微控制器 -MCU 7KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT